SDRAM: 두 판 사이의 차이

IT 위키

(새 문서: ==SDRAM의 개요== ===SDRAM(Synchronous DRAM)의 정의=== * CPU와 메모리간 액세스 타임 향상을 위해 메모리 동작 클럭을 FSB(Front Side Bus) 클럭과 동기화...) |

편집 요약 없음 |

||

| 1번째 줄: | 1번째 줄: | ||

==SDRAM의 개요== | ==SDRAM의 개요== | ||

=== | ===정의=== | ||

* CPU와 메모리간 액세스 타임 향상을 위해 메모리 동작 클럭을 FSB(Front Side Bus) 클럭과 동기화하여 데이터를 전송하는 | '''Synchronous Dynamic Random Access Memory''' | ||

* CPU와 메모리간 액세스 타임 향상을 위해 메모리 동작 클럭을 FSB(Front Side Bus) 클럭과 동기화하여 데이터를 전송하는 DRAM | |||

=== | ===특징=== | ||

{| class="wikitable" | {| class="wikitable" | ||

!특징 | !특징 | ||

| 20번째 줄: | 21번째 줄: | ||

|연속 Data Access 고속화 | |연속 Data Access 고속화 | ||

|} | |} | ||

버스 클럭의 Dual Edge에서의 데이터 전송을 통해 효율성을 높이는 DDR(Double Data Rate) SDRAM으로 발전.(현재 DDR4 SDRAM 상용화) | * 버스 클럭의 Dual Edge에서의 데이터 전송을 통해 효율성을 높이는 DDR(Double Data Rate) SDRAM으로 발전.(현재 DDR4 SDRAM 상용화) | ||

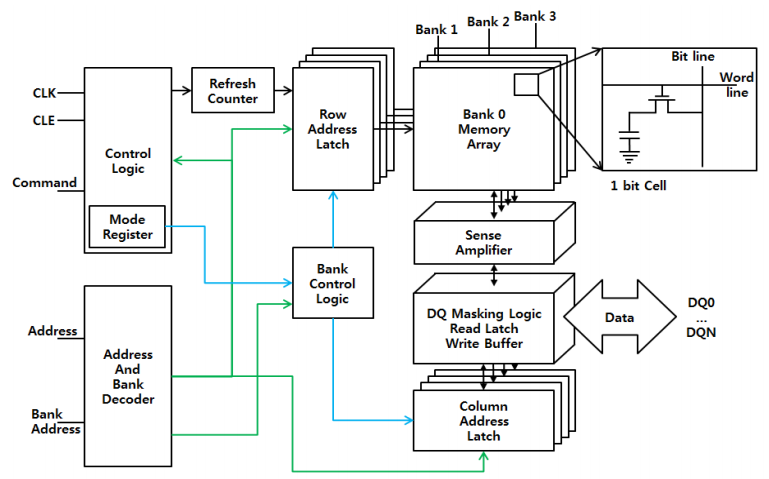

==SDRAM의 구성 및 기술 요소== | ==SDRAM의 구성 및 기술 요소== | ||

=== | ===구성=== | ||

[[image:20180503_220509.png]] | |||

* Decoded Command(Read / Write)를 수행하기 위해, RAS/CAS를 통하여 해당되는 Memory Bit Cell의 Bit line과 Word line으로 전압을 공급 | |||

===기술 요소=== | |||

{| class="wikitable" | |||

!요소 | |||

! 설명 | |||

|- | |||

| Refresh Mode | |||

|DRAM Bit-Cell의 Capacitor 내 전하의 Leakage(누수)를 보상하기 위한 재충전 과정으로 2가지 모드 존재 | |||

# Auto Refresh: 외부 Clock이 공급될 경우의 충전 | |||

# Self Refresh: CLE=0 (Power down mode)에서의 충전 | |||

|- | |||

| Precharge | |||

| Sense Amplifier를 통해 Memory Cell의 값을 읽을 수 있도록 Bit line을 VDD/2 Level로 충전하는 과정 | |||

|- | |||

| RAS(Row Address Strobe) | |||

| Latch에 의해 Bank의 행 주소를 지정할 때 발생하는 신호 | |||

|- | |||

| CAS(Column Address Strobe) | |||

| Latch에 의해 Bank의 열 주소를 지정할 때 발생하는 신호 | |||

|- | |||

| Burst Mode | |||

| Memory Cell에 인접한 영역의 Data를 연속하여 Access하는 모드. | |||

|- | |||

| Page Mode | |||

| 먼저 접근한 Row를 기억해 둔 상태에서 Column 주소만 변경하는 모드 | |||

|} | |||

* SDRAM 속도에 영향을 미치는 요소인 RAS-to-CAS delay 최소화를 위해 Fast Page Mode 등의 방식이 개발 | |||

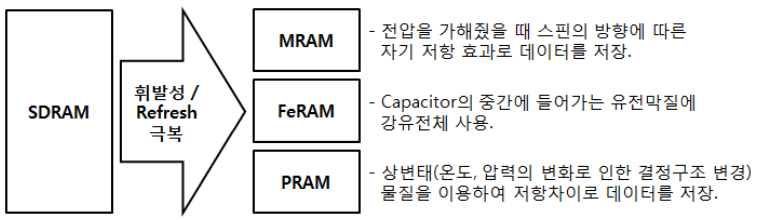

===휘발성 극복=== | |||

SDRAM의 휘발성과 Refresh 극복을 위한 비휘발성 메모리 | |||

[[image:SD램_휘발성.png]] | |||

* SDRAM의 휘발성과 Refresh로 인한 전력 소모를 최소화 위한 비휘발성 RAM 상용화 진행 중 | |||

*'''[참고] RAS-to-CAS delay와 CAS latency''' | |||

{| class="wikitable" | |||

| RAS-to-CAS delay | |||

| * 메모리에서 모든 행 주소를 읽어내는 신호인 RAS가 발생하는 시간 | |||

* RAS와 CAS사이의 지연시간이라 하며, 통상 2~3사이클이 소요 | |||

|- | |||

| CAS latency | |||

| * 메모리에서의 열 주소를 지정하는 CAS신호가 발생하여 정확한 열을 찾는 시간 | |||

* CAS 지연시간이라 하며, 통상 2~3 사이클이 소요 | |||

|} | |||

2018년 5월 3일 (목) 22:34 판

SDRAM의 개요

정의

Synchronous Dynamic Random Access Memory

- CPU와 메모리간 액세스 타임 향상을 위해 메모리 동작 클럭을 FSB(Front Side Bus) 클럭과 동기화하여 데이터를 전송하는 DRAM

특징

| 특징 | 설정 |

|---|---|

| 동기화 제어 회로 | 모든 입력과 출력이 Clock과 동기화되어 수행 |

| Multiple Bank 구조 | 다수의 Bank로 구성하여 Interleaving control 지원 |

| Command Control | Control Signal의 조합인 Command를 Decoding하여 명령 수행 |

| Burst Access | 연속 Data Access 고속화 |

- 버스 클럭의 Dual Edge에서의 데이터 전송을 통해 효율성을 높이는 DDR(Double Data Rate) SDRAM으로 발전.(현재 DDR4 SDRAM 상용화)

SDRAM의 구성 및 기술 요소

구성

- Decoded Command(Read / Write)를 수행하기 위해, RAS/CAS를 통하여 해당되는 Memory Bit Cell의 Bit line과 Word line으로 전압을 공급

기술 요소

| 요소 | 설명 |

|---|---|

| Refresh Mode | DRAM Bit-Cell의 Capacitor 내 전하의 Leakage(누수)를 보상하기 위한 재충전 과정으로 2가지 모드 존재

|

| Precharge | Sense Amplifier를 통해 Memory Cell의 값을 읽을 수 있도록 Bit line을 VDD/2 Level로 충전하는 과정 |

| RAS(Row Address Strobe) | Latch에 의해 Bank의 행 주소를 지정할 때 발생하는 신호 |

| CAS(Column Address Strobe) | Latch에 의해 Bank의 열 주소를 지정할 때 발생하는 신호 |

| Burst Mode | Memory Cell에 인접한 영역의 Data를 연속하여 Access하는 모드. |

| Page Mode | 먼저 접근한 Row를 기억해 둔 상태에서 Column 주소만 변경하는 모드 |

- SDRAM 속도에 영향을 미치는 요소인 RAS-to-CAS delay 최소화를 위해 Fast Page Mode 등의 방식이 개발

휘발성 극복

SDRAM의 휘발성과 Refresh 극복을 위한 비휘발성 메모리

- SDRAM의 휘발성과 Refresh로 인한 전력 소모를 최소화 위한 비휘발성 RAM 상용화 진행 중

- [참고] RAS-to-CAS delay와 CAS latency

| RAS-to-CAS delay | * 메모리에서 모든 행 주소를 읽어내는 신호인 RAS가 발생하는 시간

|

| CAS latency | * 메모리에서의 열 주소를 지정하는 CAS신호가 발생하여 정확한 열을 찾는 시간

|