워치독 타이머

IT 위키

- Watchdog Timer; WDT

- 비정상, 무한루프 등에 빠진 경우 시스템 통제가 불가능한 상황에서 자동으로 시스템을 리셋하는 하드웨어 기능

시그널 구성[편집 | 원본 편집]

| 시그널 | 내용 |

|---|---|

| Clear | HW 디바이스가 정상 동작함을 알려주는 주기적 Alive 신호 |

| Reset | HW 디바이스를 초기화 할 수 있는 입력 시그널 |

| Clock | HW 디바이스를 동작시키는 외부 Clock Source |

| Timeout | 타이머가 종료되었음을 알려주는 Output 신호 |

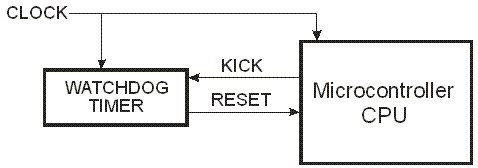

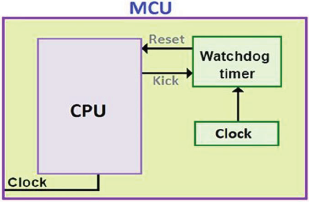

유형[편집 | 원본 편집]

| 유형 | 개념도 | 설명 |

|---|---|---|

| 내부

워치독 타이머 |

|

|

| 외부

워치독 타이머 |

|

|

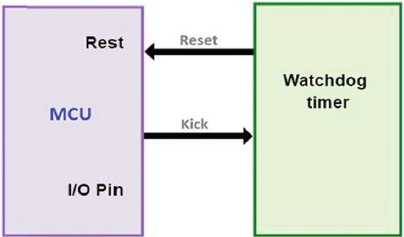

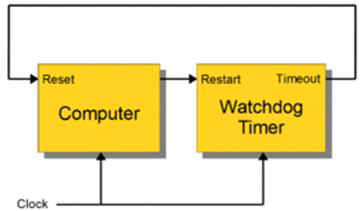

구현 방법[편집 | 원본 편집]

| 구분 | 하드웨어 설계방법 | 특징 |

|---|---|---|

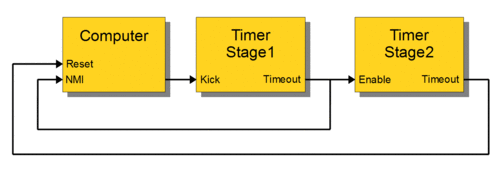

| 단단계

워치독 |

|

|

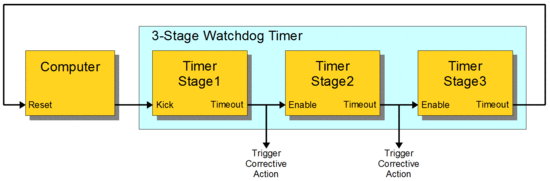

| 다단계

워치독 |

|

|

| 시정조치

로직 |

|

|